The electronics sector is nearing the limits of how many transistors can be integrated onto a computer chip’s surface. Consequently, chip manufacturers are shifting their focus from spreading out to stacking up.

Instead of the ongoing quest for ever-tinier transistors on a single plane, the industry is now pivoting towards multilayered chips. This technique resembles the transformation of a single-story ranch house into a towering skyscraper: multilayered chips can manage significantly greater quantities of data and perform complex tasks far beyond the capabilities of today’s technologies.

However, a major obstacle lies in the type of platform on which these chips are constructed. Currently, conventional silicon wafers serve as bulky scaffolding for high-quality, single-crystalline semiconducting layers. Any chip designed for stacking would need these thick silicon substrates in each layer, which would ultimately slow down inter-layer communication.

Recently, engineers from MIT have identified a solution to this challenge. They developed a novel multilayered chip design that eliminates the need for silicon wafer substrates, enabling functionality at reduced temperatures that safeguard the circuitry underneath.

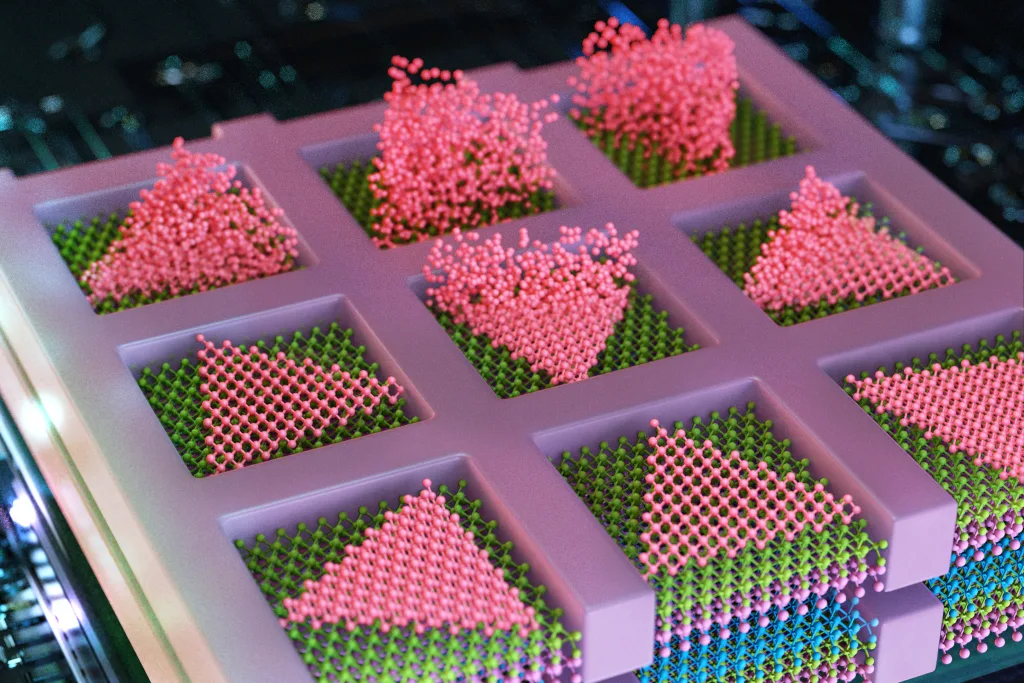

In a groundbreaking study published in Nature, the team described their innovative approach to creating multilayered chips featuring alternating layers of superior semiconducting materials that are directly stacked upon each other.

This new method allows engineers to construct high-performance transistors, along with memory and logic components, on just about any crystalline surface — not merely restricted to cumbersome silicon wafers. By doing so, the direct contact achieved between stacked semiconducting layers enhances and accelerates communication and computation, according to the researchers.

They foretell a future where this technology can lead to advanced AI hardware, represented in the form of stacked chips for laptops or wearables, boasting processing power on par with today’s supercomputers and immense data storage capabilities rivaling traditional data centers.

“This breakthrough unlocks tremendous potential for the semiconductor field, allowing chips to be stacked beyond prior limitations,” notes Jeehwan Kim, associate professor of mechanical engineering at MIT and co-author of the study. “This advancement has the potential to elevate computing power to unprecedented levels for applications across AI, memory, and logic.”

The research team included Ki Seok Kim, Seunghwan Seo, Doyoon Lee, Jung-El Ryu, Jekyung Kim, Jun Min Suh, June-chul Shin, Min-Kyu Song, Jin Feng, and Sangho Lee, alongside collaborators from Samsung Advanced Institute of Technology, Sungkyunkwan University in South Korea, and the University of Texas at Dallas.

Inspiring Foundations

This year, Kim’s group unveiled a method to cultivate high-quality semiconducting materials on amorphous surfaces, mirroring the intricate topography found in semiconducting circuits on finished chips. The materials they utilized are 2D materials known as transition-metal dichalcogenides (TMDs), which show potential as successors to silicon in crafting smaller, high-performance transistors. These 2D materials retain their semiconducting characteristics, even at atom-thin dimensions, whereas silicon tends to degrade significantly at such scales.

In prior research, the team grew TMDs on silicon wafers that had amorphous coatings, as well as atop existing TMDs. Their process involved covering a silicon wafer with a thin silicon dioxide film, patterned with tiny openings or pockets to facilitate the arrangement of atoms into high-quality single-crystalline forms, rather than allowing polycrystalline disarray to develop. However, this approach previously required high temperatures around 900 degrees Celsius.

“Growing this single-crystalline material below 400 degrees Celsius is crucial; else, the underlying circuitry risks severe damage,” Kim explains, emphasizing their goal to develop a similar approach that operates safely lower than this crucial threshold. “If we could achieve this, the impact would be immense.”

Constructing New Paths

In their latest research, Kim and his colleagues refined their technique to produce single-crystalline TMDs at lower temperatures while preserving underlying circuitry. They harnessed a concept from metallurgy: when molten metal is poured into a mold, it nucleates—forming grains that grow into an orderly crystal upon solidification. Metallurgists have discovered that nucleation at mold edges requires less energy and heat, a principle the team adapted to enhance future AI hardware.

Focusing on growing single-crystalline TMDs on a silicon wafer, already embedded with transistor circuitry, the researchers utilized a silicon dioxide mask, mirroring their preliminary work. They then applied TMD “seeds” at the edges of the mask pockets, observing that seeds at the edges grew into single-crystalline material at temperatures as low as 380 degrees Celsius, compared to those which originated from the center, which demanded higher temperatures.

Going a step further, the researchers successfully fabricated a multilayered chip with alternating TMD layers. They used molybdenum disulfide for n-type transistors and tungsten diselenide for p-type applications. Both materials achieved single-crystalline growth aligned directly, negating the need for intermediary silicon wafers altogether. Kim asserts that this breakthrough could effectively double the density of semiconducting elements within a chip, particularly metal-oxide semiconductors (CMOS), which are foundational to modern logic circuitry.

“Our technique paves the way for high-density 3D logic chips, memory, and their hybrid combinations,” affirms Kim. “Our growth-based method can facilitate the stacking of dozens to even hundreds of logic and memory layers in a manner that promotes efficient communication.”

First author Ki Seok Kim elaborates, “Traditional 3D chips are made using silicon wafers with intermediary layers, which complicates vertical alignment and limits stacking. Our growth-based method circumvents these obstacles comprehensively.”

To further commercialize their stackable chip innovation, Kim has established a new company, FS2 (Future Semiconductor 2D Materials).

“We have currently demonstrated this concept at a small-device scale. The next objective is to scale up for professional AI chip operations,” he concludes.

This pioneering research received support from the Samsung Advanced Institute of Technology and the U.S. Air Force Office of Scientific Research.

Photo credit & article inspired by: Massachusetts Institute of Technology